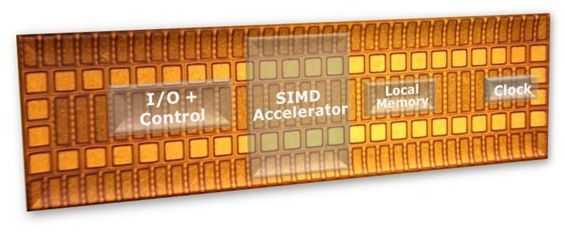

SlashGear is reporting that Intel is working on a version of something called an SIMD accelerator that will help increase graphical performance on future mobile devices. There isn’t too much to go on with the small amount of information that Intel released, but apparently the SIMD (Single Instruction, Multiple Data) accelerator that they are working on uses 10x less power than current SIMD accelerators use, making the new SIMD accelerator practical for use in handheld devices, particularly MIDs, as Intel mentions.

SlashGear is reporting that Intel is working on a version of something called an SIMD accelerator that will help increase graphical performance on future mobile devices. There isn’t too much to go on with the small amount of information that Intel released, but apparently the SIMD (Single Instruction, Multiple Data) accelerator that they are working on uses 10x less power than current SIMD accelerators use, making the new SIMD accelerator practical for use in handheld devices, particularly MIDs, as Intel mentions.

The concept of Single Instruction, Multiple Data seems somewhat contradictory to the current Atom processors which use in-order execution, but then again, I can’t claim to be an expert on CPU architecture, so these things may be unrelated. It sounds like Intel’s newer, less power hungry SIMD accelerator could be used in conjunction with their upcoming Moorestown platform.

Intel SMID accelerator aims to boost graphical performance of mobile devices http://www.umpcportal.com/?p=6360

Yes actually how the CPU and the GPU works are quite different. For instance you tend to speak of data processing for the GPU, while the CPU is executing instructions :-)

Furthermore, the in-order/out-of-order stuff has not much to do with multiple data stuff anyway.

In-order means that the only way for the CPU to run software is by processing the instructions in the order they are found in the binary file, while out-of-order means that the CPU is able to dynamically re-order the instructions to process them in a way that minimize the time spent idle (waiting for the cache buffer to fill properly for instance). It is obvious that out-of-order is very complex and so it needs a lot of stuff to work effectively, so it makes sense to choose in-order for a low-power chip. On the other hand, in theory if you’re making the binary file with the proper compiler optimization, you will end up with a binary file already ordered in the best way so that out-of-order adds no performance. In a computer, software is as much important, if not more, than the hardware…

Thanks for the crash course JP : )

SIMD is typically short for Single Instruction Multiple Data. It’s good for highly parallel applications. It’s also orthogonal to in-order/out-of-order.

You were right, it was Single Instruction, I fixed it; used to say single input.

Does this mean that we will actually be able to run graphically intensive programs. Ie Aero :-)

Isn’t part of the problem the GMA500 chipset for the Multimedia?

This isn’t gonna happen by Moorestown unless Intel has some secret plans. The Moorestown silicon taped out before this accelerator was demonstrated. We’re probably gonna see this on Larrabbee or the 32nm successor to Moorestown at the earliest.